매립 절연막을 구비하는 트랜지스터의 제조방법 및 그에 의하여 제조된 트랜지스터 [method of fabricating transistor including buried insulating layer and transistor fabricated thereby]

페이지 정보

최고관리자 0 Comments 1 Views 20-11-10 15:46 기계본문

- 기술 정보

-

-

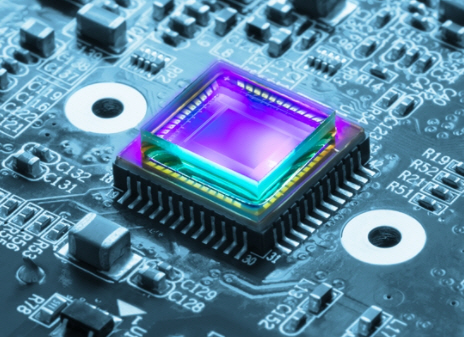

기술분야

반도체

-

현재 권리자

삼성전자 주식회사

-

Main IPC

H01L 29/78

-

존속기간 만료예정일

2024-11-26

-

출원번호

(출원일)10-2004-0098261

(2004.11.26) -

등록번호

(등록일)10-0639679

(2006.10.23)

-

기술분야

- 기술개발 목적

- - 본 발명은 트랜지스터를 제조하는 과정에서 발생하는 문제점을 해결하기 위해 창안된 것으로, 얇은 두께의 실리콘층이 요구되어 소스/드레인 영역의 두께가 감소하고 후속 공정인 실리사이드화 공정이 어려워져 직렬 저항을 갖게됨 - 그결과, 실리콘층에 단결정 실리콘층을 적용하지만 이 경우 단결정 실리콘층을 에피택셜 성장시 키는 동안 응집이 발생하는 문제가 발생함. 따라서, 트랜지스터를 제조하는 과정에서 용이하게 매 립 절연막을 형성할 수 있는 제조방법이 필요함

- 기술의 효과

- - 본 발명의 매립 절연막을 구비하는 트랜지스터는 소스/드레인 구조를 형성하기 위한 에피택셜 성장 공정 중에 소스/드레인 영역의 실리콘 표면에 응집이 발생하는 것을 억제할 수 있으며, 트랜 지스터 채널 및 소스/드레인 영역 하부에 자기정렬된 매립 절연막을 형성할 수 있음 - 또한, 트랜지스터의 채널이 유기되는 실리콘층의 양옆에 다른 격자상수를 갖는 실리콘 게르마늄 층 또는 실리콘 카바이드층을 형성함으로써 실리콘층에 가해지는 단축 변형에 의해 채널 내에서

- 적용 산업분야

-

반도체

*출처 : 첨단 헬로티

- 시장규모 및 전망

-

반도체 시장은 2019년 2,269억 달러에서 연평균 7.6% 성장하여 2025년 3,389억 달러의 규모로 전망됨

*출처 : WSTS(2020.12), IC Insights 및 수출입은행