수평 에피택시 성장을 이용하여 수직으로 적층된 나노와이어 채널을 갖는 전계효과 트랜지스터 제조방법

페이지 정보

최고관리자 0 Comments 1 Views 20-11-10 15:46 기계본문

- 분야 : 기타 개발상태 9

기술완성도

-

TRL09

사업화

- 본격적인 양산 및 사업화 단계

-

TRL08

시작품 인증/

표준화- 일부 시제품의 인증 및 인허가 취득 단계

- 조선 기자재의 경우 선급기관 인증, 의약품의 경우 식약청의 품목 허가 등

- 일부 시제품의 인증 및 인허가 취득 단계

-

TRL07

Pilot 단계 시작품

신뢰성 평가- 시작품의 신뢰성 평가

- 실제 환경(수요기업)에서 성능 검증이 이루어지는 단계

-

TRL06

Pilot 단계 시작품

성능 평가- 경제성(생산성)을 고려한, 파일로트 규모의 시작품 제작 및 평가

- 시작품 성능평가

-

TRL05

시제품 제작/

성능평가- 개발한 부품/시스템의 시작품(Prototype) 제작 및 성능 평가

- 경제성(생산성)을 고려하지 않고, 우수한 시작품을 1개~수개 미만으로 개발

-

TRL04

연구실 규모의

부품/시스템 성능평가- 연구실 규모의 부품/시스템 성능 평가가 완료된 단계

- 실용화를 위한 핵심요소기술 확보

-

TRL03

연구실 규모의

성능 검증- 연구실/실험실 규모의 환경에서 기본 성능이 검증될 수 있는 단계

- 개발하려는 시스템/부품의 기본 설계도면을 확보하는 단계

- 모델링/설계기술 확보

-

TRL02

실용 목적의 아이디어/

특허 등 개념 정립- 실용 목적의 아이디어, 특허 등 개념 정립

-

TRL01

기초 이론/

실험- 연구과제 탐색 및 기회 발굴 단계

- KEYWORD

-

FET, GAA, Si 채널, 격자상수, 수평 에피택시 성장

- 기술개요

-

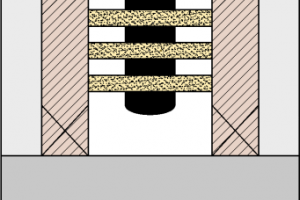

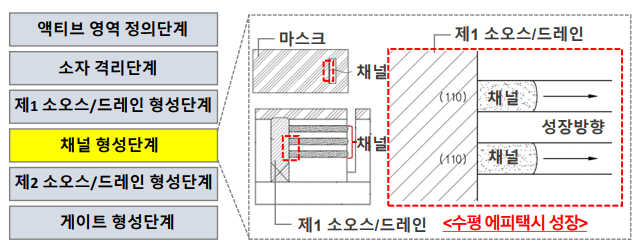

기판과의 격자상수 차이에 영향을 받지 않고 채널을 형성할 수 있도록 수평 에피택시 성장을 이용하여 수직으로 적층된 나노와이어 채널을 갖는 전계효과 트랜지스터 제조방법

- 주요 기술내용

-

• 종래기술의 문제점

게이트-올-어라운드(Gate All Around, GAA) 나노시트 Si 채널 형성방법에 있어서,

①에피택시 성장막(ex.Si/SiGe) 증착시 적층물질이 Si 기판과의 격자상수 차이에 영향 받음

②후공정에서 발생하는 Si/SiGe 인터 믹싱으로 인해 Si 채널층의 계면특성이 저하됨

• 본 기술의 해결방안

- 시장 및 기술동향

-

- 전 세계 게이트-올-어라운드 전계효과 트랜지스터(GAAFET) 시장은 2021년 약 3천만

달러에서 2030년에는 약 4억 7천만 달러로 성장할 것으로 예상되며, 예측 기간동안

35.8%의 연평균 성장률(CAGR)을 기록할 것으로 전망됨

- 반도체 트랜지스터 구조를 개선해 접촉면적을 4개 면으로 확대한 차세대 공정기술인

GAA(Gate-All-Around) 공정은 파운드리 시장의 게임체인저가 될 것으로 전망됨

- 회로 선폭이 미세화될수록 기존 핀펫 공정으로는 게이트를 통제하는 데 한계가 있을

것으로 예상되면서 이를 개선시킬 수 있는 GAA 공정이 주목 받고있음

- 기술활용 분야

-

✓ 자동차 분야 - 전기자동차, 보조운전, 자율주행, 기타 인공지능(AI) 등

전기자동차

- 기술활용 분야

-

✓ 통신 분야 - 사물인터넷(IoT), 클라우드, 5세대 이동통신(5G) 등

IoT

- 기술활용 분야

-

✓ 전자기기 분야 - 스마트폰, 게임, 웨어러블 디바이스 등

웨어러블 디바이스

- 특장점

-

- 격자상수차이영향없는채널형성可

- 수평방향으로선택적 에피택시성장하여 기판과의격자상수차이에영향을받지않음

- Si 채널층계면특성저하방지

- 채널형성과정에서단일물질을수평성장시켜 종래기술의문제점인Si/SiGe증착이후의 후공정에서발생하는Si/SiGe인터믹싱방지