채널층 보호를 위한 다중 나노쉬트의 제조방법 및 이를 이용한 게이트 올 어라운드 소자의 제조 방법

페이지 정보

최고관리자 0 Comments 1 Views 20-11-10 15:46 기계본문

- 분야 : 기타 개발상태 9

기술완성도

-

TRL09

사업화

- 본격적인 양산 및 사업화 단계

-

TRL08

시작품 인증/

표준화- 일부 시제품의 인증 및 인허가 취득 단계

- 조선 기자재의 경우 선급기관 인증, 의약품의 경우 식약청의 품목 허가 등

- 일부 시제품의 인증 및 인허가 취득 단계

-

TRL07

Pilot 단계 시작품

신뢰성 평가- 시작품의 신뢰성 평가

- 실제 환경(수요기업)에서 성능 검증이 이루어지는 단계

-

TRL06

Pilot 단계 시작품

성능 평가- 경제성(생산성)을 고려한, 파일로트 규모의 시작품 제작 및 평가

- 시작품 성능평가

-

TRL05

시제품 제작/

성능평가- 개발한 부품/시스템의 시작품(Prototype) 제작 및 성능 평가

- 경제성(생산성)을 고려하지 않고, 우수한 시작품을 1개~수개 미만으로 개발

-

TRL04

연구실 규모의

부품/시스템 성능평가- 연구실 규모의 부품/시스템 성능 평가가 완료된 단계

- 실용화를 위한 핵심요소기술 확보

-

TRL03

연구실 규모의

성능 검증- 연구실/실험실 규모의 환경에서 기본 성능이 검증될 수 있는 단계

- 개발하려는 시스템/부품의 기본 설계도면을 확보하는 단계

- 모델링/설계기술 확보

-

TRL02

실용 목적의 아이디어/

특허 등 개념 정립- 실용 목적의 아이디어, 특허 등 개념 정립

-

TRL01

기초 이론/

실험- 연구과제 탐색 및 기회 발굴 단계

- KEYWORD

-

GAA, 트랜지스터, 반도체, 고집적화, 저소비전력

- 기술개요

-

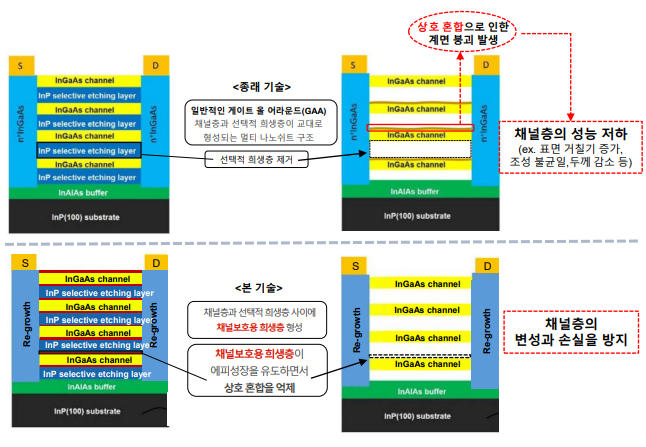

채널보호용희생층을도입하여다중나노쉬트간상호혼합억제를통해채널층보호를 위한다중나노쉬트의제조방법및이를이용한게이트올어라운드소자제조방법

- 주요 기술내용

-

- 시장 및 기술동향

-

- 전 세계 게이트 올 어라운드 FET 기술 시장 점유율은 2020년에 약 2,214만 달러였으나

2023년에는 약 4억 2,725만 달러에 이를 것이고 예측 기간동안 35.8% CAGR로 예상됨

- 게이트 올 어라운드(GAA)관련 특허는 매년 30% 가까이 증가세를 보이며 같은 기간

173건, 233건, 313건, 391건으로 증가

- 최근 삼성전자는 GAA기술을 적용한 3나노 파운드리 공정기반의 초도 양산을 시작 후

고성능 컴퓨팅용 시스템 반도체를 초도 생산한데 이어, 모바일 SoC등으로 확대 예정

- 기술활용 분야

-

✓ SoC(System on Chip)을 사용하는 모든 분야(모바일, IT, 인공지능 등)

자율주행칩

- 기술활용 분야

-

✓ 자동차 분야-자율주행시스템, 이미지 센서 구현

중앙처리장치(GPU)

- 기술활용 분야

-

✓ 컴퓨터 분야-중앙처리장치(CPU), 그래픽처리장치(GPU), 신경망처리장치(NPU) 등

인공지능(AI)

- 특장점

-

- 전류밀도의저하방지

- 후공정으로채널보호용희생층을제거한 직후, 상기채널층을 둘러싸는high-k 유전체층형성하여누설전류를방지

- 고품질소자제공可

- 채널층의 자연산화막 제거를 위한 공정이 필요 없어져 기존에 있는 채널층이 보존됨