SOI(001) 기판 상에 다종의 반도체 에피층 성장방법

페이지 정보

최고관리자 0 Comments 1 Views 20-11-10 15:46 기계본문

- 분야 : 기타 개발상태 9

기술완성도

-

TRL09

사업화

- 본격적인 양산 및 사업화 단계

-

TRL08

시작품 인증/

표준화- 일부 시제품의 인증 및 인허가 취득 단계

- 조선 기자재의 경우 선급기관 인증, 의약품의 경우 식약청의 품목 허가 등

- 일부 시제품의 인증 및 인허가 취득 단계

-

TRL07

Pilot 단계 시작품

신뢰성 평가- 시작품의 신뢰성 평가

- 실제 환경(수요기업)에서 성능 검증이 이루어지는 단계

-

TRL06

Pilot 단계 시작품

성능 평가- 경제성(생산성)을 고려한, 파일로트 규모의 시작품 제작 및 평가

- 시작품 성능평가

-

TRL05

시제품 제작/

성능평가- 개발한 부품/시스템의 시작품(Prototype) 제작 및 성능 평가

- 경제성(생산성)을 고려하지 않고, 우수한 시작품을 1개~수개 미만으로 개발

-

TRL04

연구실 규모의

부품/시스템 성능평가- 연구실 규모의 부품/시스템 성능 평가가 완료된 단계

- 실용화를 위한 핵심요소기술 확보

-

TRL03

연구실 규모의

성능 검증- 연구실/실험실 규모의 환경에서 기본 성능이 검증될 수 있는 단계

- 개발하려는 시스템/부품의 기본 설계도면을 확보하는 단계

- 모델링/설계기술 확보

-

TRL02

실용 목적의 아이디어/

특허 등 개념 정립- 실용 목적의 아이디어, 특허 등 개념 정립

-

TRL01

기초 이론/

실험- 연구과제 탐색 및 기회 발굴 단계

- KEYWORD

-

화살표 형태, 트랩핑 패턴, SOI기판, 에피층, 결함 감소, 고품위

- 기술개요

-

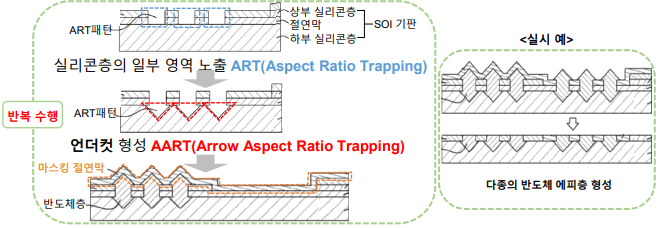

SOI기판에화살표형태의트랩핑패턴형성으로, 실리콘과반도체층간계면에서발생하는

관통전위를트랩시켜결함이없는고품질SOI 기판상에다종의반도체에피층성장방법

✓ 관통전위는 결정 결함을 일으킴

- 주요 기술내용

-

• 종래기술의 문제점

Si 기판상에Ⅲ-Ⅴ화합물 반도체를 성장시키는데 있어, Si 기판과 Ⅲ-Ⅴ

화합물반도체 간의 격자상수 부정합과 계면상의 결정 결함 문제 발생

⇒ 실용성 저하 및 반도체의 성능 저하

• 본 기술의 해결방안

- 시장 및 기술동향

-

- 전세계화합물반도체시장규모는2021-2025년예측기간중6.33%의CAGR로확대되고,

115억3,000만달러의성장이전망됨

- 실리콘기반반도체소자한계를극복하기위해실리콘보다전자이동속도가5~10배이상

빠르고전력소모량도10배이상적은화합물반도체가실리콘대체물질로각광받고있음

- 화합물 반도체에 대한 많은 연구와 투자가 이루어지고 있으며, 고전력 솔루션에 대한

수요가 증가하고 있음

- 기술활용 분야

-

✓ 광학분야–LED,태양전지,이미지센서용포토디텍터등

태양전지

- 기술활용 분야

-

✓ 통신분야-무선네트워킹,사물인터넷(IoT),5G,Wi-Fi등

5G 이동통신

- 기술활용 분야

-

✓ 반도체소자 분야-광소자, 전자소자 등

Wi-Fi

- 특장점

-

- 결함감소

- 실리콘면이노출된화살표형태의트랩핑 패턴을형성하여, 실리콘과반도체층간의 계면에서발생하는관통전위를트랩시켜 결함이없는대면적의반도체소자제공

- 에피성장용이

- 기판상에ART 방법을사용하여에피 성장시,낮은구조물을이용하더라도넓은 부위의에피성장이 용이