조기 항복전압을 막을 수 있는 p-n접합 반도체 소자 및 그 제조방법

페이지 정보

최고관리자 0 Comments 1 Views 20-11-10 15:46 기계본문

- 분야 : 기타 개발상태 9

기술완성도

-

TRL09

사업화

- 본격적인 양산 및 사업화 단계

-

TRL08

시작품 인증/

표준화- 일부 시제품의 인증 및 인허가 취득 단계

- 조선 기자재의 경우 선급기관 인증, 의약품의 경우 식약청의 품목 허가 등

- 일부 시제품의 인증 및 인허가 취득 단계

-

TRL07

Pilot 단계 시작품

신뢰성 평가- 시작품의 신뢰성 평가

- 실제 환경(수요기업)에서 성능 검증이 이루어지는 단계

-

TRL06

Pilot 단계 시작품

성능 평가- 경제성(생산성)을 고려한, 파일로트 규모의 시작품 제작 및 평가

- 시작품 성능평가

-

TRL05

시제품 제작/

성능평가- 개발한 부품/시스템의 시작품(Prototype) 제작 및 성능 평가

- 경제성(생산성)을 고려하지 않고, 우수한 시작품을 1개~수개 미만으로 개발

-

TRL04

연구실 규모의

부품/시스템 성능평가- 연구실 규모의 부품/시스템 성능 평가가 완료된 단계

- 실용화를 위한 핵심요소기술 확보

-

TRL03

연구실 규모의

성능 검증- 연구실/실험실 규모의 환경에서 기본 성능이 검증될 수 있는 단계

- 개발하려는 시스템/부품의 기본 설계도면을 확보하는 단계

- 모델링/설계기술 확보

-

TRL02

실용 목적의 아이디어/

특허 등 개념 정립- 실용 목적의 아이디어, 특허 등 개념 정립

-

TRL01

기초 이론/

실험- 연구과제 탐색 및 기회 발굴 단계

- KEYWORD

-

가장자리, 반곡면, 경사면, 공핍층, 두께, 조기 항복전압

- 기술개요

-

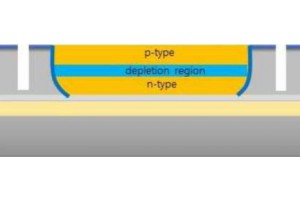

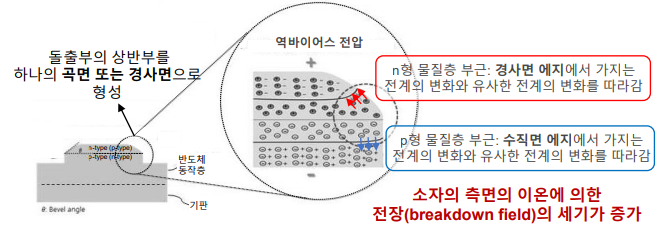

반도체 소자의 가장자리 면 부분을 반곡면 또는 경사면 형태로 형성하여, 소자의 가장자리 면의 공핍층 두께를 두껍게 확장시켜 소자의 조기 항복전압을 막을 수 있는 p-n 접합 반도체 소자 및 그 제조방법

- 주요 기술내용

-

• 종래기술의 문제점

일반적으로가장자리면수직형(edge surface vertical type)의p-n 접합모델의경우,소자 측면의 결함이 다량 존재하여 공핍층 두께를 상대적으로 감소시키고, 이온에 의한 전장의 세기를 감소시킴 ⇒ 조기 에지 항복전압(premature edge breakdown) 발생

• 본 기술의 해결방안

- 시장 및 기술동향

-

- 세계 박막 반도체 증착 시장 규모는 2020-2027년간 13.5%의 연평균 복합 성장률(CAGR)로

성장할 전망이며, 2027년에는391억 달러에 달할 것으로 예측됨

- 이방성 식각 기술은 초미세화 혹은 고밀도가 요구되는 MEMS 소자 등과 같은 차세대 제품에

매우 중요한 기술이기 때문에 높은 수준의 식각 기술에 대한 시장의 수요가 높음

- 역방향 전류에 의한 신뢰성 특성을 요구하는 소자 또는 애벌란시 다이오드(valanche diode)

특성을 가진 소자 등은 위의 식각 기술을 필요로 하며, p-n 접합 설계에 따른 식각 구조의

응용이 필요하여 개발이 활발히 진행중임

- 기술활용 분야

-

✓ LED분야-일반조명및특수조명,디스플레이,가전제품용표시소자,자동차용조명등

디스플레이

- 기술활용 분야

-

✓ 통신분야-전자부품,컴퓨터,영상,음향및통신장비등

자동차 조명

- 기술활용 분야

-

✓ 트랜지스터-양극성 접합 트랜지스터, MOSFET, 박막 트랜지스터, CMOS로 등

FUJIFILM 社 카메라 내 내장된 CMOS

- 특장점

-

- 항복전압억제

- 반도체 소자의 가장자리 면의 공핍층 두께를 벌크(bulk) 영역에 비해 상대적으로 더 두껍게 확장하여 반도체 소자의 조기 항복전압을 억제할 수 있음

- 소자성능향상

- 가장자리 면 부분에 5~10º경사면이 있어 단차 피복이 우수한 산화 처리가 가능 → 전류 붕괴 현상 개선