## METHOD FOR MANUFACTURING LOW POWER AND HIGH PERFORMANCE SEMICONDUCTOR DEVICE

**Affiliation:** Korea university Type of Partnership: Open for negotiation Cost: Open for negotiation

Researcher Information: Sang-sig Kim / Department of Electronics Engineering Contact Person: Jung-eun Kim / 02-3290-5837 / jekim2018@korea.ac.kr

# Si NW Poly

SiO<sub>2</sub>

(Substrate of bulk silicon nanowire)

substrate 200 nm

#### Abstract

The present invention is related to a semiconductor device and a method of fabricating the same, and more particularly, to an energy efficient semiconductor device fabricated by a nanowire and a method of fabrication the same.

#### **Problems with Existing Technology**

Technologies to reduce the subthreshold leakage current by reducing a subthreshold swing of the MOSFET are being researched.

- To implement the soft device having various forms, the soft device should be produced by using various forms or nanomaterials such as nanowires, nanoparticles, organic materials, etc., deviating from the typical bulk based device development.

- To implement an energy efficient soft device, the nanowire which has excellent electrical characteristics and may implement soft characteristics is largely preferred in the research field.

#### **Technology Readiness Level**

TRL 3: Experimental Proof of Concept

| TRL1                            | TRL2                                | TRL3                                | TRL4                              | TRL5                                                  | TRL6                                                     | TRL7        | TRL8                       | TRL9                              |

|---------------------------------|-------------------------------------|-------------------------------------|-----------------------------------|-------------------------------------------------------|----------------------------------------------------------|-------------|----------------------------|-----------------------------------|

| Basic<br>Technology<br>Research | Technology<br>Concept<br>formulated | Experimental<br>Proof of<br>Concept | Technology<br>validated<br>in lab | Technology<br>validated in<br>relevant<br>environment | Technology<br>demonstrated<br>in relevant<br>environment | operational | System complete& qualified | Full<br>commercial<br>application |

#### Differentiation and Effect

#### Differentiation

#### Configuration of semiconductor device using nanowire

- It can solve the problems of an increase in a leakage current occurring from a short channel effect of a typical MOSFET and a subthreshold swing value of 60 mV/dec or higher due to a structural limitation.

- It have the average subthreshold swing of at least 30.2 mV/dec, so the switching characteristic may be improved due to this electrical characteristic.

#### **Effect of Technology**

### The present invention overcomes the disadvantage of the typical semiconductor device

- The technology may have value for companies who manufacture semiconductor components.

- The power consumption problem, which typical MOSFET devices have, is solved so that portability is maximized and the performance of the electronic device may be improved from the improvement in the switching characteristic.

## KOREA UNIVERSITY

#### **Technology Application Field**

Mobile phones, TVs, portable devices, medical devices, wearable smart devices, etc.

#### **Market Trends**

<Scale of semiconductor market>

- The size of the domestic semiconductor market is expected to reach 4,693 billion won in 2013 and 5,670 billion won in 2019.

- The global semiconductor market is expected to reach

\$ 315.5 billion in 2013 and \$ 378.3 billion in 2019.

#### **Technology Implementation**

#### Method of manufacturing semiconductor device

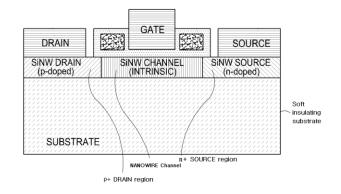

- A semiconductor device of FIG. 1 includes a soft insulation substrate, a p+-i-n+ semiconductor nanowire, an insulation layer, source/drain metal electrodes, a gate electrode structure, which covers only a part among an intrinsic channel region and a metal or semiconductor nanoparticle electric charge trap spacer

- The semiconductor nanowire 120, which is for a FBFET (Feedback field-effect transistor), has p+, i, n+ impurities injected by using a photolithography and an ion injection process.

<FIG.1 A cross sectional view and a picture of a semiconductor device fabricated on a plastic substrate by using a single crystal semiconductor nanowire>

#### List of related patents

| No. | Title of Invention                                                       | Patent No./<br>Application No. |  |

|-----|--------------------------------------------------------------------------|--------------------------------|--|

| 1   | SEMICONDUCTOR DEVICE AND METHOD OF FABRICATING SAME                      | US 14/604,127                  |  |

| 2   | LOGIC SEMICONDUCTOR DEVICES                                              | US 15/870,092                  |  |

| 3   | DUAL GATE SEMICONDUCTOR MEMORY DEVICE WITH VERTICAL SEMICONDUCTOR COLUMN | US 15/185,388                  |  |